fix(sim-verilator): Renamed the filenames that are inconsistent with the readme usage |

||

|---|---|---|

| .github | ||

| dependencies | ||

| docs | ||

| sim-verilator | ||

| ventus | ||

| .gitignore | ||

| .gitmodules | ||

| CHANGELOG.md | ||

| GPGPU_output_diff.py | ||

| LICENSE | ||

| LICENSE.Berkeley | ||

| LICENSE.apache | ||

| Makefile | ||

| NOTICE | ||

| README.md | ||

| build.sc | ||

| common.sc | ||

| mill | ||

| shell.nix | ||

README.md

Ventus(乘影) GPGPU

GPGPU processor supporting RISCV-V extension, developed with Chisel HDL.

Copyright 2021-2024 by International Innovation Center of Tsinghua University, Shanghai.

We are calling for contributors. If you are interested in Ventus GPGPU, please contact yff22@mails.tsinghua.edu.cn.

“乘影”在RVV编译器工具链、验证环境开发和硬件设计方面还有很多不足,如果您有意愿参与到“乘影”的开发中,欢迎在github上pull request,也欢迎联系 yff22@mails.tsinghua.edu.cn。

乘影2.0架构文档在这里,添加了对OpenCL支持所需的改动。如果您在软硬件方面有任何建议,欢迎提issue或邮件联系。

乘影开源GPGPU项目网站:opengpgpu.org.cn。

Home page of Ventus-GPGPU project: opengpgpu.org.cn.

乘影软件工具链release版本在这里获取。

You can get the release version of software toolchain here.

Architecture

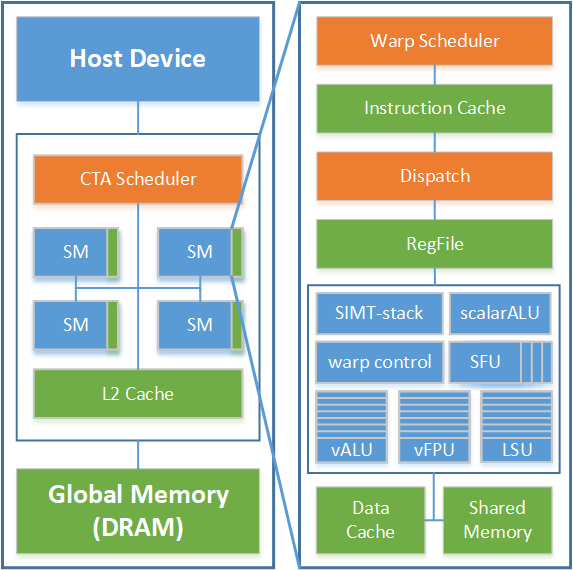

The micro-architecture overview of Ventus(乘影) is shown below.

ISA and micro-architecture docs is here. Chinese docs is here.

OpenCL C compiler based on LLVM is developed by Terapines(兆松科技).

Use the script in ventus-llvm to configure the complete software toolchain, including isa-simulator, pocl and driver.

Quick Start

如果你需要从头开始配置WSL和IDEA的开发环境,可以参考中文教程从零开始的配置教程。这个教程的部分命令已经过时,但依然是很好的参考。

The tutorial of Chisel development environment configuration comes from chipsalliance/playground: chipyard in mill :P

- Install dependencies and setup environments:

- Arch Linux

pacman -Syu --noconfirm make parallel wget cmake ninja mill dtc verilator git llvm clang lld protobuf antlr4 numactl - Nix

nix-shell - Ubuntu

apt-get install gcc g++ make parallel wget cmake verilator git llvm clang lld protobuf-compiler antlr4 numactl

We recomment using java 17 or higher versions. We test the project under java 19.

- Clone project, init and update dependencies

git clone https://github.com/THU-DSP-LAB/ventus-gpgpu.git

make init

-

IDE support

make ideaormake bsp # generate IDE bsp -

to generate verilog file, use

make verilog. The output file isGPGPU_top.v. -

to run tests, use

make test. Output waveform file is attest_run_dir. Due to the limitations ofchiseltest, we have customized another simulation framework based on Verilator. Please refer to thesim-verilatorfolder's README for more details.

Understanding Program Output in Our Project

This section is dedicated to explaining the output generated by our program, which is crucial for developers who wish to understand the inner workings or debug the software. The output is structured to provide detailed insights into the program's execution, including instruction addresses, operations on warp units, and register manipulations.

Warp Execution Output

The program output is like:

warp 3 0x800001d4 0x0042a303 x 6 90000000

warp 3identifies the warp unit in action, which start from 0.0x800001d4specifies the virtual address of the instruction being executed.0x0042a303represents the instruction itself.x 6 90000000signifies an operation where the program writes the value90000000to scalar register 6 of warp 3.

For a more complex example:

warp 2 0x80000200 0x0002a2fb v 5 0001 00000000 00000000 00000000 be8d0fac

v 5 0001indicates an operation on vector register 5 of the second warp, where0001is a mask specifying that only the last thread is active.- The data

be8d0facis written to the last element of the vector register due to the mask setting.

Jump Instructions

The output related to jump instructions follows this format:

warp 1 0x80000490 0x00008067 Jump? 1 800002f4

Jump? 1 800002f4indicates a conditional jump to the address0x800002f4depending on the evaluation of the preceding condition.

Load/Store Instructions

Load and store operations are crucial for reading from and writing to memory:

warp 2 0x80000200 0x0002a2fb lsu.r v 5 op 3 @ 00000000 bdcccccd 3e54ad4b 90002038

warp 2 0x80000200 0x0002a2fb v 5 0001 00000000 00000000 00000000 be8d0fac

lsu.rspecifies a load operation from memory into a register.@ 90002038marks the memory addresses from which data is loaded.v 5 0001 00000000 00000000 00000000 be8d0facrepresents the data is loaded, and only the last element of v[5] is set tobe8d0facdue to the mask (and apparently only90002038is a valid address).

For write operations:

warp 2 0x80000240 0x0052607b lsu.w v 5 op 3 mask 0001 00000000 bdcccccd 3e54ad4b 3f0e5e0a @ 00000000 90000034 90000038 9000003c

warp 2 0x80000240 0x0052607b lsu.w fin

Branching Output

Branch-related outputs are essential for SIMT arch support. Example:

warp 3 0x80000248 0x0483305b setrpc 0x8000028c

warp 3 0x8000024c 0x0401905b vbranch current mask and npc: 0001 0x80000250

warp 3 0x8000028c 0x0000205b join mask and npc: 1110 0x8000028c pop stack ? 1

Acknowledgement

We refer to some open-source design when developing Ventus GPGPU.

| Sub module | Source | Detail |

|---|---|---|

| CTA scheduler | MIAOW | Our CTA scheduler module is based on MiaoW ultra-threads dispatcher. |

| L2Cache | block-inclusivecache-sifive | Our L2Cache design is inspired by Sifive's block-inclusivecache |

| Multiplier | XiangShan | We reused Array Multiplier in XiangShan. FPU design is also inspired by XiangShan. |

| Config, ... | rocket-chip | Some modules are sourced from RocketChip |

License and Project Origin

This repository is licensed under the Mulan Permissive Software License, Version 2 (Mulan PSL v2), except for certain files which are licensed under different terms.

-

build.sc,common.scandshell.nixare licensed under the Apache License, Version 2.0. These files were originally derived from the chipsalliance/playground repository. While these files served as the foundation, the build system has since undergone significant evolution. -

ventus/src/config/config.scalais licensed under the Apache License, Version 2.0. -

ventus/src/pipeline/ALU.scalais licensed under both the Apache License, Version 2.0 and the BSD 3-Clause License, reflecting its origins from the rocket-chip repository.

For more details, please see the NOTICE file and the headers of the respective files.